Unité arithmétique et logique - Arithmetic logic unit

| Fait partie d'une série sur | |||||||

| circuits logiques arithmétiques | |||||||

|---|---|---|---|---|---|---|---|

| Navigation Rapide | |||||||

|

Composants

|

|||||||

|

Voir également |

|||||||

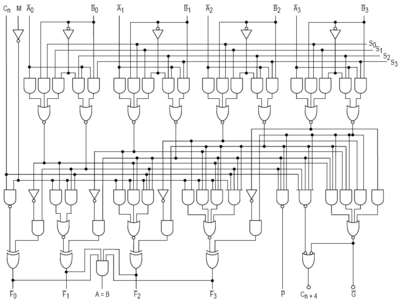

En informatique , une unité arithmétique et logique (ALU) est un circuit numérique combinatoire qui effectue des opérations arithmétiques et au niveau du bit sur des nombres binaires entiers . Cela contraste avec une unité à virgule flottante (FPU), qui fonctionne sur des nombres à virgule flottante . C'est un élément fondamental de nombreux types de circuits informatiques, y compris l' unité centrale de traitement (CPU) des ordinateurs, les FPU et les unités de traitement graphique (GPU).

Les entrées d'une ALU sont les données à opérer, appelées opérandes , et un code indiquant l'opération à effectuer ; la sortie de l'ALU est le résultat de l'opération effectuée. Dans de nombreuses conceptions, l'ALU a également des entrées ou des sorties d'état, ou les deux, qui transmettent des informations sur une opération précédente ou l'opération en cours, respectivement, entre l'ALU et les registres d'état externes .

Signaux

Une ALU a une variété de réseaux d'entrée et de sortie , qui sont les conducteurs électriques utilisés pour transmettre des signaux numériques entre l'ALU et les circuits externes. Lorsqu'une ALU fonctionne, des circuits externes appliquent des signaux aux entrées de l'ALU et, en réponse, l'ALU produit et transmet des signaux aux circuits externes via ses sorties.

Données

Une ALU de base possède trois bus de données parallèles constitués de deux opérandes d' entrée ( A et B ) et d'une sortie de résultat ( Y ). Chaque bus de données est un groupe de signaux qui véhicule un nombre entier binaire. Typiquement, les largeurs de bus A, B et Y (le nombre de signaux composant chaque bus) sont identiques et correspondent à la taille de mot native du circuit externe (par exemple, l'unité centrale d'encapsulation ou un autre processeur).

Code opération

Le code d' opération d' entrée est un bus parallèle qui transmet à l'unité ALU un code de sélection d'opération, qui est une valeur énumérée qui spécifie la ou opération arithmétique logique désirée devant être exécutées par l'unité ALU. La taille de l'opcode (sa largeur de bus) détermine le nombre maximum d'opérations différentes que l'ALU peut effectuer ; par exemple, un code opération à quatre bits peut spécifier jusqu'à seize opérations ALU différentes. Généralement, un opcode ALU n'est pas le même qu'un opcode en langage machine , bien que dans certains cas, il puisse être directement encodé en tant que champ de bits dans un opcode en langage machine.

Statut

Les sorties

Les sorties d'état sont divers signaux individuels qui transmettent des informations supplémentaires sur le résultat de l'opération ALU en cours. Les ALU à usage général ont généralement des signaux d'état tels que :

- Carry-out , qui véhicule le report résultant d'une opération d'addition, l'emprunt résultant d'une opération de soustraction, ou le bit de débordement résultant d'une opération de décalage binaire.

- Zero , qui indique que tous les bits de Y sont des zéros logiques.

- Négatif , qui indique que le résultat d'une opération arithmétique est négatif.

- Overflow , qui indique que le résultat d'une opération arithmétique a dépassé la plage numérique de Y.

- Parité , qui indique si un nombre pair ou impair de bits dans Y est un logique.

À la fin de chaque opération ALU, les signaux de sortie d'état sont généralement stockés dans des registres externes pour les rendre disponibles pour les futures opérations ALU (par exemple, pour implémenter l'arithmétique à précision multiple ) ou pour contrôler le branchement conditionnel . La collection de registres de bits qui stockent les sorties d'état est souvent traitée comme un seul registre à plusieurs bits, appelé « registre d'état » ou « registre de code de condition ».

Contributions

Les entrées d'état permettent de mettre des informations supplémentaires à la disposition de l'ALU lors de l'exécution d'une opération. Typiquement, il s'agit d'un seul bit de « report » qui est le report stocké d'une opération ALU précédente.

Fonctionnement du circuit

Un ALU est un circuit logique combinatoire , ce qui signifie que ses sorties changeront de manière asynchrone en réponse aux changements d'entrée. En fonctionnement normal, des signaux stables sont appliqués à toutes les entrées ALU et, lorsqu'un temps suffisant (appelé « délai de propagation ») s'est écoulé pour que les signaux se propagent à travers le circuit ALU, le résultat de l'opération ALU apparaît sur l'ALU les sorties. Les circuits externes connectés à l'ALU sont chargés d'assurer la stabilité des signaux d'entrée de l'ALU tout au long de l'opération et de laisser suffisamment de temps aux signaux pour se propager à travers l'ALU avant d'échantillonner le résultat de l'ALU.

En général, des circuits externes contrôlent une ALU en appliquant des signaux à ses entrées. Typiquement, le circuit externe utilise une logique séquentielle pour contrôler le fonctionnement de l'ALU, qui est rythmé par un signal d'horloge d'une fréquence suffisamment basse pour garantir suffisamment de temps pour que les sorties ALU se stabilisent dans les pires conditions.

Par exemple, une CPU commence une opération d'ajout d'ALU en acheminant les opérandes de leurs sources (qui sont généralement des registres) vers les entrées d'opérandes de l'ALU, tandis que l' unité de contrôle applique simultanément une valeur à l'entrée du code d'opération de l'ALU, la configurant pour effectuer l'addition. Dans le même temps, la CPU achemine également la sortie de résultat ALU vers un registre de destination qui recevra la somme. Les signaux d'entrée de l'ALU, qui sont maintenus stables jusqu'à la prochaine horloge, sont autorisés à se propager à travers l'ALU et vers le registre de destination pendant que la CPU attend la prochaine horloge. Lorsque l'horloge suivante arrive, le registre de destination stocke le résultat ALU et, étant donné que l'opération ALU est terminée, les entrées ALU peuvent être configurées pour la prochaine opération ALU.

Les fonctions

Un certain nombre de fonctions arithmétiques et logiques binaires de base sont généralement prises en charge par les ALU. Les ALU de base à usage général incluent généralement ces opérations dans leurs répertoires :

Opérations arithmétiques

- Additionner : A et B sont additionnés et la somme apparaît en Y et continuez.

- Additionner avec retenue : A, B et retenue sont additionnées et la somme apparaît en Y et retenue.

- Soustraire : B est soustrait de A (ou vice versa) et la différence apparaît en Y et en exécution. Pour cette fonction, le report est effectivement un indicateur "d'emprunt". Cette opération peut également être utilisée pour comparer les grandeurs de A et B ; dans ce cas, la sortie Y peut être ignorée par le processeur, qui ne s'intéresse qu'aux bits d'état (notamment zéro et négatif) qui résultent de l'opération.

- Soustraire avec emprunt : B est soustrait de A (ou vice versa) avec emprunt (report) et la différence apparaît en Y et en report (emprunt).

- Complément à deux (négation) : A (ou B) est soustrait de zéro et la différence apparaît en Y.

- Incrément : A (ou B) est augmenté de un et la valeur résultante apparaît en Y.

- Décrément : A (ou B) est diminué de un et la valeur résultante apparaît en Y.

- Pass through : tous les bits de A (ou B) apparaissent non modifiés en Y. Cette opération est typiquement utilisée pour déterminer la parité de l'opérande ou s'il est nul ou négatif, ou pour charger l'opérande dans un registre du processeur.

Opérations logiques au niveau du bit

- ET : le ET au niveau du bit de A et B apparaît en Y.

- OU : le OU au niveau du bit de A et B apparaît en Y.

- OU exclusif : le XOR bit à bit de A et B apparaît en Y.

- Complément à un : tous les bits de A (ou B) sont inversés et apparaissent en Y.

Opérations de décalage de bits

| Taper | La gauche | Droite |

|---|---|---|

| Décalage arithmétique |

|

|

| Changement logique |

|

|

| Tourner |

|

|

| Rotation à travers le transport |

|

|

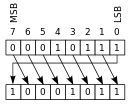

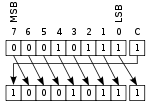

Des opérations de décalage ALU provoquent opérande A (ou B) à décalage à gauche ou à droite ( en fonction de l'opcode) et l'décalée opérande apparaît à Y. simple UMM peuvent généralement décaler l'opérande par une seule position de bit, tandis que UMM plus complexes emploient décalage circulaire qui leur permettre de décaler l'opérande d'un nombre arbitraire de bits en une seule opération. Dans toutes les opérations de décalage d'un seul bit, le bit décalé de l'opérande apparaît lors de l'exécution ; la valeur du bit décalé dans l'opérande dépend du type de décalage.

- Décalage arithmétique : l'opérande est traité comme unentier complément à deux , ce qui signifie que le bit le plus significatif est un bit de "signe" et est conservé.

- Décalage logique : un zéro logique est décalé dans l'opérande. Ceci est utilisé pour décaler des entiers non signés.

- Rotation : l'opérande est traité comme un tampon circulaire de bits de sorte que ses bits de poids faible et de poids fort sont effectivement adjacents.

- Rotate through carry : le bit de report et l'opérande sont traités collectivement comme un tampon circulaire de bits.

Applications

Arithmétique multi-précision

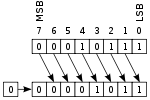

Dans les calculs arithmétiques d'entiers, l'arithmétique à précision multiple est un algorithme qui opère sur des entiers qui sont plus grands que la taille du mot ALU. Pour ce faire, l'algorithme traite chaque opérande comme une collection ordonnée de fragments de taille ALU, classés du plus significatif (MS) au moins significatif (LS) ou vice versa. Par exemple, dans le cas d'une ALU 8 bits, l'entier 24 bits 0x123456serait traité comme une collection de trois fragments 8 bits : 0x12(MS) 0x34, et 0x56(LS). Puisque la taille d'un fragment correspond exactement à la taille du mot ALU, l'ALU peut opérer directement sur ce "morceau" d'opérande.

L'algorithme utilise l'ALU pour opérer directement sur des fragments d'opérande particuliers et ainsi générer un fragment correspondant (un "partiel") du résultat multi-précision. Chaque partiel, lorsqu'il est généré, est écrit dans une région de stockage associée qui a été désignée pour le résultat à précision multiple. Ce processus est répété pour tous les fragments d'opérande afin de générer une collection complète de partiels, qui est le résultat de l'opération de précision multiple.

Dans les opérations arithmétiques (par exemple, addition, soustraction), l'algorithme commence par invoquer une opération ALU sur les fragments LS des opérandes, produisant ainsi à la fois un bit partiel LS et un bit d'exécution. L'algorithme écrit le partiel dans la mémoire désignée, tandis que la machine d'état du processeur stocke généralement le bit d'exécution dans un registre d'état ALU. L'algorithme passe ensuite au fragment suivant de la collection de chaque opérande et invoque une opération ALU sur ces fragments avec le bit de report stocké de l'opération ALU précédente, produisant ainsi un autre partiel (plus significatif) et un bit d'exécution. Comme auparavant, le bit de retenue est stocké dans le registre d'état et le partiel est écrit dans la mémoire désignée. Ce processus se répète jusqu'à ce que tous les fragments d'opérande aient été traités, résultant en une collection complète de partiels en stockage, qui constituent le résultat arithmétique multi-précision.

Dans les opérations de décalage à précision multiple, l'ordre de traitement des fragments d'opérande dépend de la direction du décalage. Dans les opérations de décalage à gauche, les fragments sont traités LS en premier parce que le bit LS de chaque partiel - qui est acheminé via le bit de report stocké - doit être obtenu à partir du bit MS de l'opérande moins significatif précédemment décalé à gauche. Inversement, les opérandes sont traités MS d'abord dans les opérations de décalage à droite car le bit MS de chaque partiel doit être obtenu à partir du bit LS de l'opérande plus significatif précédemment décalé à droite.

Dans les opérations logiques au niveau du bit (par exemple, ET logique, OU logique), les fragments d'opérande peuvent être traités dans n'importe quel ordre arbitraire car chaque partiel ne dépend que des fragments d'opérande correspondants (le bit de report stocké de l'opération ALU précédente est ignoré).

Opérations complexes

Bien qu'une ALU puisse être conçue pour exécuter des fonctions complexes, la complexité du circuit, le coût, la consommation d'énergie et la plus grande taille qui en résultent rendent cela peu pratique dans de nombreux cas. Par conséquent, les ALU sont souvent limitées à des fonctions simples qui peuvent être exécutées à des vitesses très élevées (c'est-à-dire des délais de propagation très courts), et le circuit du processeur externe est chargé d'exécuter des fonctions complexes en orchestrant une séquence d'opérations ALU plus simples.

Par exemple, le calcul de la racine carrée d'un nombre peut être implémenté de différentes manières, en fonction de la complexité de l'ALU :

- Calcul en une seule horloge : une ALU très complexe qui calcule une racine carrée en une seule opération.

- Pipeline de calcul : un groupe d'ALU simples qui calcule une racine carrée par étapes, avec des résultats intermédiaires passant par des ALU disposées comme une ligne de production d' usine. Ce circuit peut accepter de nouveaux opérandes avant de terminer les précédents et produit des résultats aussi rapides que l'ALU très complexe, bien que les résultats soient retardés de la somme des délais de propagation des étages ALU. Pour plus d'informations, consultez l'article sur le pipeline d'instructions .

- Calcul itératif : une ALU simple qui calcule la racine carrée en plusieurs étapes sous la direction d'une unité de contrôle .

Les implémentations ci-dessus passent de la plus rapide et la plus chère à la plus lente et la moins coûteuse. La racine carrée est calculée dans tous les cas, mais les processeurs avec des ALU simples prendront plus de temps pour effectuer le calcul car plusieurs opérations ALU doivent être effectuées.

Mise en œuvre

Une ALU est généralement implémentée soit en tant que circuit intégré (CI) autonome , tel que le 74181 , soit en tant que partie d'un CI plus complexe. Dans ce dernier cas, une ALU est typiquement instanciée en la synthétisant à partir d'une description écrite en VHDL , Verilog ou un autre langage de description matérielle . Par exemple, le code VHDL suivant décrit une ALU 8 bits très simple :

entity alu is

port ( -- the alu connections to external circuitry:

A : in signed(7 downto 0); -- operand A

B : in signed(7 downto 0); -- operand B

OP : in unsigned(2 downto 0); -- opcode

Y : out signed(7 downto 0)); -- operation result

end alu;

architecture behavioral of alu is

begin

case OP is -- decode the opcode and perform the operation:

when "000" => Y <= A + B; -- add

when "001" => Y <= A - B; -- subtract

when "010" => Y <= A - 1; -- decrement

when "011" => Y <= A + 1; -- increment

when "100" => Y <= not A; -- 1's complement

when "101" => Y <= A and B; -- bitwise AND

when "110" => Y <= A or B; -- bitwise OR

when "111" => Y <= A xor B; -- bitwise XOR

when others => Y <= (others => 'X');

end case;

end behavioral;

Histoire

Le mathématicien John von Neumann a proposé le concept ALU en 1945 dans un rapport sur les fondations d'un nouvel ordinateur appelé EDVAC .

Le coût, la taille et la consommation électrique des circuits électroniques étaient relativement élevés tout au long de l'enfance de l' ère de l' information . Par conséquent, tous les ordinateurs série et de nombreux premiers ordinateurs, tels que le PDP-8 , avaient une simple ALU qui fonctionnait sur un bit de données à la fois, bien qu'ils présentaient souvent une taille de mot plus large aux programmeurs. L'un des premiers ordinateurs à avoir plusieurs circuits ALU discrets à un seul bit était le Whirlwind I de 1948 , qui employait seize de ces « unités mathématiques » pour lui permettre de fonctionner sur des mots de 16 bits.

En 1967, Fairchild a introduit la première ALU implémentée sous forme de circuit intégré, le Fairchild 3800, composé d'une ALU à huit bits avec accumulateur. D'autres ALU à circuits intégrés ont rapidement fait leur apparition, notamment des ALU à quatre bits telles que les Am2901 et 74181 . Ces dispositifs étaient généralement capables de « tranche de bits », ce qui signifie qu'ils avaient des signaux « d'anticipation » qui facilitaient l'utilisation de plusieurs puces ALU interconnectées pour créer une ALU avec une taille de mot plus large. Ces dispositifs sont rapidement devenus populaires et ont été largement utilisés dans les mini-ordinateurs bit-slice.

Les microprocesseurs ont commencé à apparaître au début des années 1970. Même si les transistors étaient devenus plus petits, l'espace de matrice était souvent insuffisant pour une ALU pleine largeur et, par conséquent, certains premiers microprocesseurs utilisaient une ALU étroite qui nécessitait plusieurs cycles par instruction en langage machine. Les exemples incluent le populaire Zilog Z80 , qui a effectué des ajouts de huit bits avec une ALU de quatre bits. Au fil du temps, les géométries des transistors ont encore diminué, suivant la loi de Moore , et il est devenu possible de construire des ALU plus larges sur des microprocesseurs.

Les transistors à circuit intégré (CI) modernes sont des ordres de grandeur plus petits que ceux des premiers microprocesseurs, ce qui permet d'installer des ALU très complexes sur les circuits intégrés. Aujourd'hui, de nombreuses ALU modernes ont de grandes largeurs de mots et des améliorations architecturales telles que des décaleurs en barillet et des multiplicateurs binaires qui leur permettent d'effectuer, en un seul cycle d'horloge, des opérations qui auraient nécessité plusieurs opérations sur les ALU antérieures.

Les ALU peuvent être réalisées sous forme de circuits mécaniques , électromécaniques ou électroniques et, ces dernières années, des recherches sur les ALU biologiques ont été menées (par exemple, à base d' actine ).

Voir également

- Additionneur (électronique)

- Unité de génération d'adresses (AGU)

- Unité de chargement-stockage

- Multiplicateur binaire

- Unité d'exécution

Les références

Lectures complémentaires

- Hwang, Enoch (2006). Conception de logique numérique et de microprocesseur avec VHDL . Thomson. ISBN 0-534-46593-5.

- Stallings, William (2006). Organisation et architecture informatiques : conception pour la performance (7e éd.). Pearson Prentice Hall. ISBN 0-13-185644-8.