IBM 7030 Stretch - IBM 7030 Stretch

| IBM Stretch | |

|---|---|

Console de maintenance IBM 7030 au Musée des Arts et Métiers , Paris

| |

| Concevoir | |

| Fabricant | IBM |

| Designer | Gene Amdahl |

| Date de sortie | Mai 1961 |

| Unités vendues | 9 |

| Prix | 7 780 000 $ US (équivalent à 67 380 000 $ en 2020) |

| Enveloppe | |

| Poids | 70 000 livres (35 tonnes courtes; 32 t) |

| Puissance | 100 kW à 110 V |

| Système | |

| Système opérateur | MCP |

| CPU | Processeur 64 bits |

| Mémoire | 2048 kilo-octets (262144 x 64 bits) |

| MIPS | 1.2 MIPS |

L' IBM 7030 , également connu sous le nom de Stretch , était le premier supercalculateur à transistors d' IBM . C'était l'ordinateur le plus rapide au monde de 1961 jusqu'à ce que le premier CDC 6600 soit devenu opérationnel en 1964.

Conçu à l'origine pour répondre à une exigence formulée par Edward Teller du Lawrence Livermore National Laboratory , le premier exemplaire a été livré au Los Alamos National Laboratory en 1961, et une seconde version personnalisée, l' IBM 7950 Harvest , à la National Security Agency en 1962. à l' établissement de recherche sur les armes atomiques à Aldermaston , en Angleterre , a été fortement utilisé par les chercheurs là - bas et à AERE Harwell , mais seulement après le développement du compilateur S2 Fortran qui a été le premier à ajouter des matrices dynamiques , et qui a ensuite été porté sur l' Atlas Ferranti de Laboratoire informatique Atlas à Chilton.

Le 7030 était beaucoup plus lent que prévu et n'a pas atteint ses objectifs de performance agressifs. IBM a été contraint de baisser son prix de 13,5 millions de dollars à seulement 7,78 millions de dollars et a retiré le 7030 des ventes aux clients au-delà de ceux ayant déjà négocié des contrats. Le magazine PC World a nommé Stretch l'un des plus gros échecs de gestion de projet de l' histoire de l' informatique .

Au sein d'IBM, être éclipsé par la plus petite Control Data Corporation semblait difficile à accepter. Le chef de projet, Stephen W. Dunwell, a d'abord été désigné comme bouc émissaire pour son rôle dans "l'échec", mais comme le succès de l' IBM System/360 est devenu évident, il a reçu des excuses officielles et, en 1966, a été nommé IBM Compagnon .

Malgré l'échec de Stretch à atteindre ses propres objectifs de performances, il a servi de base à de nombreuses caractéristiques de conception du système IBM/360 à succès, qui a été livré en 1964.

Historique du développement

Au début de 1955, le Dr Edward Teller du Laboratoire de rayonnement de l' Université de Californie voulait un nouveau système de calcul scientifique pour les calculs hydrodynamiques tridimensionnels . Des propositions ont été demandées à IBM et à UNIVAC pour ce nouveau système, qui s'appellera Livermore Automatic Reaction Calculator ou LARC . Selon le directeur d'IBM Cuthbert Hurd , un tel système coûterait environ 2,5 millions de dollars et fonctionnerait à un ou deux MIPS . La livraison devait intervenir deux à trois ans après la signature du contrat.

Chez IBM, une petite équipe de Poughkeepsie comprenant John Griffith et Gene Amdahl a travaillé sur la proposition de conception. Juste après qu'ils aient terminé et qu'ils étaient sur le point de présenter la proposition, Ralph Palmer les a arrêtés et leur a dit : « C'est une erreur. La conception proposée aurait été construite avec des transistors à contact ponctuel ou des transistors à barrière de surface , tous deux susceptibles d'être bientôt dépassés par le transistor à diffusion alors nouvellement inventé .

IBM est retourné à Livermore et a déclaré qu'ils se retiraient du contrat et a proposé à la place un système nettement meilleur : « Nous n'allons pas construire cette machine pour vous ; nous voulons construire quelque chose de mieux ! Nous ne savons pas exactement ce qu'il faudra. mais nous pensons que ce sera un autre million de dollars et une autre année, et nous ne savons pas à quelle vitesse cela fonctionnera, mais nous aimerions tirer dix millions d'instructions par seconde." Livermore n'a pas été impressionné, et en mai 1955, ils ont annoncé qu'UNIVAC avait remporté le contrat LARC , maintenant appelé Livermore Automatic Research Computer . Le LARC sera finalement livré en juin 1960.

En septembre 1955, craignant que le Laboratoire national de Los Alamos ne commande également un LARC, IBM a soumis une proposition préliminaire pour un ordinateur binaire hautes performances basé sur la version améliorée de la conception que Livermore avait rejetée, qu'ils ont reçue avec intérêt. En janvier 1956, le projet Stretch a été officiellement lancé. En novembre 1956, IBM remporte le contrat avec l'objectif de performance agressif d'une « vitesse au moins 100 fois supérieure à celle d' IBM 704 » (soit 4 MIPS). La livraison était prévue pour 1960.

Lors de la conception, il s'est avéré nécessaire de réduire les vitesses d'horloge, indiquant clairement que Stretch ne pouvait pas atteindre ses objectifs de performances agressifs, mais les estimations de performances variaient de 60 à 100 fois l'IBM 704. En 1960, le prix de 13,5 millions de dollars a été fixé pour l'IBM 7030. En 1961, les références réelles indiquaient que les performances de l'IBM 7030 n'étaient qu'environ 30 fois supérieures à celles de l'IBM 704 (c'est-à-dire 1,2 MIPS), provoquant une gêne considérable pour IBM. En mai 1961, Tom Watson a annoncé une baisse de prix de tous les 7030 en cours de négociation à 7,78 millions de dollars et le retrait immédiat du produit des ventes futures.

Son temps d'addition à virgule flottante est de 1,38 à 1,50 microsecondes , le temps de multiplication est de 2,48 à 2,70 microsecondes et le temps de division est de 9,00 à 9,90 microsecondes.

Impact technique

Bien que l'IBM 7030 n'ait pas été considéré comme un succès, il a engendré de nombreuses technologies intégrées dans les futures machines qui ont connu un grand succès. La logique de transistor du système modulaire standard était à la base de la gamme d'ordinateurs scientifiques IBM 7090 , des ordinateurs commerciaux IBM 7070 et 7080 , des gammes IBM 7040 et IBM 1400 et du petit ordinateur scientifique IBM 1620 ; le 7030 utilisait environ 170 000 transistors. Les unités de stockage de base IBM 7302 modèle I ont également été utilisées dans les IBM 7090, IBM 7070 et IBM 7080. La multiprogrammation , la protection de la mémoire, les interruptions généralisées, l' octet de huit bits pour les E/S étaient tous des concepts incorporés plus tard dans l' IBM System/360 gamme d'ordinateurs ainsi que la plupart des unités centrales de traitement (CPU) plus récentes.

Stephen Dunwell, le chef de projet qui est devenu un bouc émissaire lorsque Stretch a échoué commercialement, a souligné peu de temps après le lancement phénoménal de System/360 en 1964 que la plupart de ses concepts de base ont été lancés par Stretch. En 1966, il avait reçu des excuses et avait été nommé IBM Fellow, un grand honneur qui comportait les ressources et l'autorité nécessaires pour poursuivre les recherches souhaitées.

Le pipeline d'instructions , la prélecture et le décodage, et l' entrelacement de mémoire ont été utilisés dans des conceptions ultérieures de superordinateurs telles que les modèles IBM System/360 91 , 95 et 195 , et la série IBM 3090 ainsi que des ordinateurs d'autres fabricants. En 2021, ces techniques sont toujours utilisées dans la plupart des microprocesseurs avancés, à commencer par la génération des années 1990 qui comprenait l'Intel Pentium et le Motorola/IBM PowerPC , ainsi que dans de nombreux microprocesseurs et microcontrôleurs embarqués de divers fabricants.

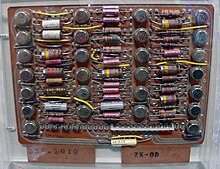

Implémentation matérielle

Le processeur 7030 utilise une logique à couplage d'émetteurs (appelée à l'origine logique de pilotage de courant ) sur 18 types de cartes de système modulaire standard (SMS). Il utilise 4 025 cartes doubles (comme illustré) et 18 747 cartes simples, contenant 169 100 transistors, nécessitant une puissance totale de 21 kW. Il utilise des transistors à dérive de germanium NPN et PNP à grande vitesse , avec une fréquence de coupure supérieure à 100 MHz et utilisant environ 50 mW chacun. Certains circuits de troisième niveau utilisent un troisième niveau de tension. Chaque niveau logique a un retard d'environ 20 ns. Pour gagner en vitesse dans les zones critiques, une logique émetteur-suiveur est utilisée pour réduire le retard à environ 10 ns.

Il utilise la même mémoire centrale que l' IBM 7090 .

Installations

- Laboratoire scientifique de Los Alamos (LASL) en avril 1961, accepté en mai 1961 et utilisé jusqu'au 21 juin 1971.

- Lawrence Livermore National Laboratory , Livermore, Californie livré en novembre 1961.

- Agence de sécurité nationale des États- Unis en février 1962 en tant que processeur principal du système IBM 7950 Harvest , utilisé jusqu'en 1976, lorsque le système de bande IBM 7955 Tractor a développé des problèmes en raison de cames usées qui ne pouvaient pas être remplacées.

- Atomic Weapons Establishment , Aldermaston , Angleterre, livré en février 1962

- US Weather Bureau Washington DC, livré en juin/juillet 1962.

- MITRE Corporation , livré en décembre 1962. et utilisé jusqu'en août 1971. Au printemps 1972, il est vendu à l'université Brigham Young , où il est utilisé par le département de physique jusqu'à sa mise au rebut en 1982.

- US Navy Dahlgren Naval Proving Ground , livré en septembre/octobre 1962.

- Commissariat à l'énergie atomique , France, rendu en novembre 1963.

- IBM.

L'IBM 7030 du Lawrence Livermore Laboratory (à l'exception de sa mémoire centrale ) et des parties de l'IBM 7030 MITRE Corporation/Brigham Young University résident maintenant dans la collection du Computer History Museum , à Mountain View, en Californie .

Architecture

Formats de données

- Les nombres à virgule fixe sont de longueur variable, stockés au format binaire (1 à 64 bits) ou décimal (1 à 16 chiffres) et au format non signé ou au format signe/grandeur . Au format décimal, les chiffres sont des octets de longueur variable (4 à 8 bits).

- Les nombres à virgule flottante ont un indicateur d'exposant de 1 bit, un exposant de 10 bits, un signe d'exposant de 1 bit, une magnitude de 48 bits et un octet de signe de 4 bits au format signe/magnitude.

- Les caractères alphanumériques sont de longueur variable et peuvent utiliser n'importe quel code de caractère de 8 bits ou moins.

- Les octets sont de longueur variable (1 à 8 bits).

Format d'instruction

Les instructions sont soit 32 bits, soit 64 bits.

Registres

Les registres recouvrent les 32 premières adresses de la mémoire comme indiqué.

| ! Adresse | Mnémonique | S'inscrire | Stocké dans: |

|---|---|---|---|

| 0 | $Z | Zéro 64 bits : se lit toujours comme zéro, ne peut pas être modifié par des écritures | Stockage principal |

| 1 | $IT | temporisateur d'intervalle (bits 0..18): décrémenté à 1024 Hz, se recycle environ toutes les 8,5 minutes, à zéro il allume l'"indicateur de signal temporel" dans le registre indicateur | Stockage de base d'index |

| $TC | Horloge 36 bits (bits 28..63) : nombre de ticks de 1024 Hz, les bits 38..63 incrémentent une fois par seconde, se recycle tous les ~777 jours. | ||

| 2 | $IA | Adresse d'interruption 18 bits | Stockage principal |

| 3 | $UB | Adresse limite supérieure 18 bits (bits 0-17) | Registre à transistors |

| $LB | Adresse de limite inférieure de 18 bits (bits 32-49) | ||

| Contrôle de limite 1 bit (bit 57) : détermine si les adresses à l'intérieur ou à l'extérieur des adresses de limite sont protégées | |||

| 4 | Bits de maintenance 64 bits : utilisés uniquement pour la maintenance | Stockage principal | |

| 5 | $CA | adresse de canal (bits 12..18) : en lecture seule, définie par le "échange", un processeur d'e/s | Registre à transistors |

| 6 | $CPU | autres bits CPU (bits 0..18) : mécanisme de signalisation pour un cluster jusqu'à 20 CPU | Registre à transistors |

| 7 | $LZC | nombre de zéros à gauche (bits 17..23) : nombre de bits zéro non significatifs à partir d'un résultat de connexion ou d'une opération à virgule flottante | Registre à transistors |

| $AOC | nombre de tout-uns (bits 44..50) : nombre de bits définis dans le résultat conjonctif ou multiple décimal ou diviser | ||

| 8 | $L | Moitié gauche de l' accumulateur 128 bits | Registre à transistors |

| 9 | $R | Moitié droite de l'accumulateur 128 bits | |

| dix | $SB | octet de signe de l'accumulateur (bits 0..7) | |

| 11 | $IND | registre indicateur (bits 0..19) | Registre à transistors |

| 12 | $MASQUE | Registre de masque de 64 bits : bits 0..19 toujours 1, bits 20..47 inscriptibles, bits 48..63 toujours 0 | Registre à transistors |

| 13 | $RM | Registre de reste de 64 bits : défini uniquement par des instructions de division d'entier et de virgule flottante | Stockage principal |

| 14 | $FT | Registre de facteur 64 bits : modifié uniquement par l'instruction « facteur de charge » | Stockage principal |

| 15 | $TR | Registre de transit 64 bits | Stockage principal |

| 16 ... 31 |

$X0 ... $X15 |

Registres d'index 64 bits (seize) | Stockage de base d'index |

L'accumulateur et les registres d'index fonctionnent au format signe et grandeur .

Mémoire

La mémoire principale est de 16K à 256K de mots binaires de 64 bits, dans des banques de 16K.

La mémoire a été chauffée/refroidie à l'huile par immersion pour stabiliser ses caractéristiques de fonctionnement.

Logiciel

- Programme d'assemblage STRETCH (STRAP)

- MCP (à ne pas confondre avec le Burroughs MCP )

- Langages de programmation COLASL et IVY

- langage de programmation FORTRAN

Voir également

- IBM 608 , le premier appareil informatique transistorisé disponible dans le commerce

- ILLIAC II , un super ordinateur transistorisé de l' Université de l'Illinois qui rivalisait avec Stretch.

Remarques

Les références

Lectures complémentaires

- Brooks, Frédéric (2010). "L'étirement est un excellent exercice, il vous met en forme pour gagner". IEEE Annales de l'histoire de l'informatique . 32 : 4-9. doi : 10.1109/MAHC.2010.26 . S2CID 43480009 .

Liens externes

- Entretien d'histoire orale avec Gene Amdahl Charles Babbage Institute , Université du Minnesota, Minneapolis. Amdahl discute de son rôle dans la conception de plusieurs ordinateurs pour IBM, notamment STRETCH, IBM 701 , 701A et IBM 704 . Il discute de son travail avec Nathaniel Rochester et la direction d'IBM du processus de conception des ordinateurs.

- IBM Stretch Collections @ Computer History Museum

- 7030 Système de traitement des données (Archives IBM)

- IBM Stretch (alias système de traitement de données IBM 7030)

- Croquis d'organisation d'IBM Stretch

- Rapport BRL sur IBM Stretch

- Planification d'un système informatique – Projet Stretch , livre de 1962.

- Documents IBM 7030 sur Bitsavers.org (fichiers PDF)