Texas Instruments TMS9900 - Texas Instruments TMS9900

| Designer | Texas Instruments |

|---|---|

| Morceaux | 16 bits |

| Introduit | 1976 |

| Concevoir | SCRC |

| Endianité | Gros |

| Registres | |

| PC, WP, ST | |

| Usage général | 2 situés en interne dans le processeur (WP, ST) pile 16 × 16 bits située dans la RAM externe |

Lancé en juin 1976, le TMS9900 était l'un des premiers microprocesseurs 16 bits à puce unique disponibles dans le commerce . Il a mis en œuvre Texas Instruments de TI-990 minicomputer architecture dans un format puce unique, et a été initialement utilisée pour les modèles bas de gamme de cette gamme.

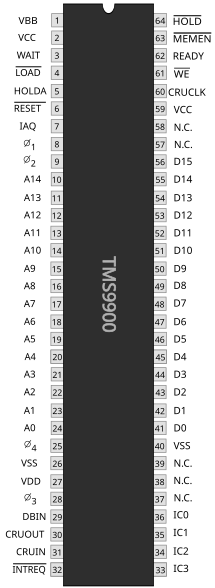

Son format DIP à 64 broches le rendait plus coûteux à mettre en œuvre dans des machines plus petites que le format plus courant à 40 broches, et il a vu relativement peu de gains de conception en dehors de l'utilisation propre de TI. Parmi ces utilisations figurait l' ordinateur domestique TI-99/4 de TI , qui s'est finalement vendu à environ 2,8 millions d'exemplaires.

Au milieu des années 1980, le domaine des micro-ordinateurs se déplaçait vers des systèmes 16 bits comme l' Intel 8088 et des conceptions 16/32 bits plus récentes comme le Motorola 68000 , qui surpassaient facilement les 9900 et étaient généralement moins chers. Sans avenir évident pour la puce, TI a tourné son attention vers des processeurs à usage spécial comme le Texas Instruments TMS320 , introduit en 1983.

Histoire

Le TMS9900 a été conçu comme une version à puce unique de la série de mini-ordinateurs TI 990 , tout comme l' Intersil 6100 était un PDP-8 à puce unique (12 bits), et le Fairchild 9440 et le Data General mN601 étaient tous deux des versions à une puce de Data General. 's Nova . Contrairement aux microprocesseurs 16 bits multipuces tels que le National Semiconductor IMP-16 ou le DEC LSI-11 , dont certains étaient antérieurs au TMS9900, ce dernier était un microprocesseur 16 bits autonome à puce unique. La seule conception connue à puce unique 16 bits qui précède le TMS9900 est le presque inconnu Panafacom MN1610 , sorti en 1975.

Les racines du mini-ordinateur du TMS9900 donnent lieu à un certain nombre de caractéristiques architecturales que l'on ne trouve pas couramment sur les conceptions qui ont commencé à partir d'une feuille vierge. Parmi celles-ci, notons l'utilisation par le TMS9900 de registres mappés dans la mémoire principale . Cela permet une commutation de contexte rapide , qui peut être accomplie en changeant un seul pointeur, alors que des conceptions plus traditionnelles nécessiteraient le stockage de l'ensemble des registres internes dans la mémoire ou la pile. L'inconvénient de cette approche est que l'accès à ces registres prend plus de temps. Dans une implémentation de mini-ordinateur, l'effet est relativement faible et l'avantage dans un environnement multitâche est important. Dans d'autres rôles, comme les micro-ordinateurs mono-utilisateur ou les systèmes embarqués, ce compromis peut ne pas valoir la peine.

TI a utilisé la même architecture dans différentes divisions pour une synergie d'entreprise : « une entreprise, une architecture informatique ». À la fin des années 1970, Walden C. Rhines a présenté le TMS9900 à un groupe IBM développant un ordinateur personnel. "Nous ne saurions qu'en 1981 ce que nous avions perdu", car IBM a choisi l' Intel 8088 pour le PC IBM , se souvient-il. Après l'échec de la tentative d'entrer sur le marché des ordinateurs personnels avec des produits tels que le TI-99/4A , la division des microprocesseurs de l'entreprise s'est finalement tournée vers la série de processeurs spéciaux TMS320 .

Architecture

Le TMS9900 possède trois registres internes de 16 bits : compteur de programme (PC), registre d'état (ST) et registre de pointeur d'espace de travail (WP). Le registre WP pointe vers une adresse de base dans la RAM externe où les 16 registres utilisateur à usage général du processeur (chacun de 16 bits de large) sont conservés. Cette architecture permet un changement de contexte rapide ; Par exemple, lorsqu'un sous - programme est entré, seul le registre de l'espace de travail unique doit être modifié au lieu d'exiger que les registres soient enregistrés individuellement.

Les adresses font référence aux octets avec la convention d'ordre big endian . Le TMS9900 est une machine 16 bits classique avec un espace d'adressage de 2 16 octets (65 536 octets ou 32 768 mots).

Il n'y a pas de concept de pile ni de registre de pointeur de pile. Au lieu de cela, il existe des instructions de branchement qui enregistrent le compteur de programme dans un registre et modifient le contexte du registre. Les 16 vecteurs d'interruption matériels et les 16 vecteurs logiciels consistent chacun en une paire de valeurs PC et WP, de sorte que le changement de contexte de registre est également effectué automatiquement par une interruption.

Jeu d'instructions et adressage

Le TMS9900 dispose de 69 instructions d'un, deux ou trois mots et toujours alignées sur les mots en mémoire. Le jeu d'instructions est assez orthogonal , ce qui signifie qu'à quelques exceptions près, les instructions peuvent utiliser toutes les méthodes d'accès aux opérandes (modes d'adressage).

Les modes d'adressage incluent Immédiat (opérande dans l'instruction), Direct ou "Symbolique" (adresse de l'opérande dans l'instruction), Registre (opérande dans le registre de l'espace de travail), Registre indirect (adresse de l'opérande dans le registre de l'espace de travail) avec ou sans auto-incrémentation, Indexé (adresse de l'opérande dans l'instruction indexée avec le contenu du registre de l'espace de travail) et relatif au compteur de programme.

Les instructions à double opérande les plus importantes (ajouter, soustraire, comparer, déplacer, etc.) contiennent un mode d'adressage à 2 bits et des champs de sélecteur de registre à 4 bits pour les opérandes source et de destination. Dans l'opcode, le mode "Symbolique" est représenté en mode indexé avec le champ de registre défini sur 0, par conséquent le registre de l'espace de travail 0 (WR0) ne peut pas être utilisé en mode indexé. Dans les instructions à double opérande moins fréquemment utilisées comme XOR, l'opérande de destination doit être un registre d'espace de travail (ou une paire de registres d'espace de travail dans le cas des instructions de multiplication et de division).

Le contrôle de flux est facilité par un groupe d'une instruction Jump inconditionnelle et de douze instructions Jump conditionnelles. Les cibles de saut sont relatives au PC avec un décalage de -128 à +127 adresses de mots.

Pour les appels de sous-programme, l'instruction Brancher et charger le pointeur d'espace de travail (BLWP) charge les nouvelles valeurs WP et PC, puis enregistre les valeurs de WP, PC et ST dans les (nouveaux) registres 13, 14 et 15 respectivement. A la fin de la sous-routine, le Return Workspace Pointer (RTWP) les restaure dans l'ordre inverse. En utilisant BLWP/RTWP, il est possible d'imbriquer des appels de sous-programme malgré l'absence d'une pile, cependant, le programmeur doit affecter explicitement l'espace de travail de registre approprié.

Le jeu d'instructions contient également un opcode Branch and Link (BL) qui enregistre uniquement le PC dans le registre 11 sans modifier le WP. Dans ce cas, une instruction de branchement (B) utilisant WR11 comme adresse de destination peut servir d'opcode de retour, mais les sous-programmes de type BL ne peuvent pas être imbriqués sans que le programmeur prenne des mesures pour enregistrer l'adresse de retour.

Le TMS9900 prend en charge une instruction d'exécution "X" (eXecute). Cette instruction exécute l'instruction dans un registre. Il peut être utilisé pour le débogage (en tant qu'instruction de point d'arrêt ) et pour créer des tables d'opcodes indexés comme celles utilisées dans les interpréteurs de byte-code.

Le TMS9900 prend également en charge l'instruction eXtended OPeration (XOP). XOP reçoit un nombre compris entre 0 et 15 ainsi qu'une adresse source. Lorsqu'elle est invoquée, l'instruction effectuera un changement de contexte à travers l'un des seize vecteurs à des emplacements prédéfinis dans la mémoire. Ceci est similaire à une interruption, mais l'instruction XOP stocke également l'adresse source dans le registre 11 du nouvel espace de travail. XOP est moins flexible qu'un BLWP, car les vecteurs de transfert doivent être à des emplacements fixes, mais économise de la mémoire, car l'adresse source peut être utilisée par le sous-programme exécuté à la place, lorsqu'il ne définit pas l'emplacement du vecteur. XOP est utilisé pour implémenter des instructions dans le logiciel dans les modèles bas de gamme, où les versions haut de gamme de la série de mini-ordinateurs 990 peuvent avoir du matériel dédié pour les exécuter.

Dans les comparaisons typiques avec l' Intel 8086 , le TMS9900 avait des programmes plus petits. Les seuls inconvénients étaient le petit espace d'adressage et le besoin de RAM rapide.

Mise en œuvre

Le TMS9900 a été mis en œuvre dans un processus MOS à grille en silicium à canal N, qui nécessitait des alimentations +5 V, -5 V et +12 V et une horloge à quatre phases (sans chevauchement) avec une fréquence maximale de 3 MHz (333 ns cycle), généralement généré à partir d'un cristal de 48 MHz à l'aide d'une puce génératrice d'horloge TIM9904 (aka 74LS362).

Les instructions les plus courtes nécessitent huit cycles d'horloge ou 2,7 s pour se terminer (en supposant 0 cycles d'attente externes), de nombreuses autres s'exécutent entre 10 et 14 cycles (3,3...4,7 s) ; l'instruction la plus longue (DIV) peut prendre jusqu'à 124 cycles (41,3 s).

La puce était emballée dans un DIP (alors inhabituel) de 64 broches et de 0,9" de large . Le nombre relativement important de broches permettait au bus d'adresses 15 bits (mot) et au bus de données 16 bits d'être sortis sur des broches dédiées sans l'utilisation du multiplexage (contrairement au processeur Intel 8086, par exemple ), en gardant les connexions de mémoire externe simples. Contrairement à la convention utilisée par de nombreux autres fabricants, TI a marqué les lignes d'adresse et de données les plus significatives "A0" et "D0", respectivement. Tous internes les chemins de données et l' ALU ont une largeur de 16 bits.

Le processeur peut être mis en pause avec le bus d'adresse à trois états pour un accès direct à la mémoire externe (DMA). Les accès à la mémoire ont toujours une largeur de 16 bits, le CPU effectuant automatiquement des opérations de lecture avant écriture pour les accès à l'échelle de l'octet.

Le système d'interruption matérielle prend en charge une entrée de priorité d'interruption de 4 bits, qui devait être supérieure au niveau de priorité stocké dans le registre d'état (bits 12 à 15) pour que la demande d'interruption soit satisfaite. De plus, l' entrée /LOAD fournit une fonction d'interruption non masquable avec un vecteur dédié.

Le processeur TMS9900 contient également un registre à décalage de 16 bits ("CRU") conçu pour l'interfaçage avec des registres à décalage externes, avec des instructions dédiées prenant en charge l'accès aux champs de 1 à 16 bits de largeur sur un total de 4096 bits adressables.

Des périphériques parallèles peuvent être connectés de manière mappée en mémoire à l'adresse et au bus de données normaux.

Applications

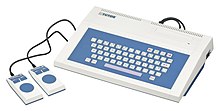

Le TMS9900 a été utilisé dans les ordinateurs personnels TI-99/4 et TI-99/4A . Malheureusement, pour réduire les coûts de production, TI a choisi d'utiliser dans ces systèmes seulement 128 mots de 16 bits du type de RAM rapide auquel le TMS9900 pouvait accéder directement. Le reste de la mémoire était constitué de 16 Ko de DRAM 8 bits qui n'était accessible qu'indirectement via le contrôleur d'affichage vidéo, ce qui a paralysé les performances de la TI-99/4.

TI a développé la série TM990 de modules informatiques, comprenant le processeur, la mémoire, les E/S, qui, lorsqu'ils sont branchés sur un châssis de carte, peuvent former un mini-ordinateur 16 bits. Ceux-ci étaient généralement utilisés pour le contrôle des processus. Un entraîneur de microprocesseur a été publié sous la forme du TM990/189.

Développement de produits de la famille TMS9900

La deuxième génération de la famille de microprocesseurs TMS9900 était le TMS9995 qui offrait « des performances fonctionnelles à des vitesses 3 fois plus rapides que n'importe quel processeur précédent de la famille 9900 », en grande partie grâce à l'inclusion de la technologie de prélecture d'instructions. Dans le domaine de l'informatique domestique, le TMS9995 n'a été utilisé que dans le Tomy Tutor , une mise à niveau ésotérique TI99-4/A appelée Geneve 9640 , et un projet publié dans Electronics Today : le Powertran Cortex. Il était prévu qu'il soit utilisé dans les systèmes informatiques TI-99/2 et TI-99/8, mais aucun n'a dépassé le stade du prototype.

TI a ensuite développé la famille de microprocesseurs TMS99000 plus puissante, qui a été utilisée comme CPU dans le mini-ordinateur 990/10A pour réduire les coûts. Malheureusement, au moment où le 990/10A est arrivé sur le marché, la fin de l'ère des mini-ordinateurs était déjà en vue.

La famille TMS99000 comprend deux microprocesseurs, le TMS99105A et le TMS99110A, qui sont identiques à l'exception de l'inclusion d'une mémoire ROM de macrostore sur puce (la mémoire de macrostore contient des fonctions ou des instructions supplémentaires via des routines d'émulation écrites en code machine standard). Le macrostore ROM sur puce du microprocesseur TMS99110A contient des instructions à virgule flottante qui sont disponibles dans le jeu d'instructions en langage machine, tandis que le TMS99105A n'inclut pas de macrostore ROM. Un troisième membre de la famille TMS99000, le TMS99120, a été annoncé mais n'a peut-être jamais été produit commercialement. Le macrostore ROM sur puce du TMS99120 contient des routines de prise en charge d'exécution pour le langage de haut niveau PASCAL.

Le jeu d'instructions pour la famille TMS99000 est un sur-ensemble du TMS9995 et du TMS9900, avec compatibilité de code objet. Les instructions supplémentaires comprennent celles pour la multiplication et la division signées ; décalage, addition et soustraction de mots longs ; registre d'état de chargement, pointeur de lieu de travail de chargement, opérations de pile, prise en charge multiprocesseur, manipulation de bits. Les membres de la famille peuvent accéder instantanément à 256 Ko de mémoire et peuvent utiliser le mappeur de mémoire TIM99610 pour adresser jusqu'à 16 Mo. L'architecture contient de nombreuses autres avancées par rapport aux TMS9900 et TMS9995.

Variantes

| Modèle | La description |

|---|---|

| TI990/9 | Premier processeur multi-puce pour les systèmes de mini-ordinateurs, 1974 |

| TI990/10 | Implémentation multi-puces pour les systèmes de mini-ordinateurs, 1975 |

| TI990/12 | Implémentation multi-puces, plus rapide que 990/10 |

| TMS9900 | Implémentation à puce unique, 1976, utilisée dans l'ordinateur TI-99/4(A) |

| TMS9940 | Microcontrôleur avec ROM 2Ko, RAM 128B, décrémenteur, bus CRU, 1979 |

| TMS9980 TMS9981 |

Versions 8 bits du TMS9900 |

| TMS9985 | TMS9940 avec 8 Ko de ROM, 256 Go de RAM et un bus externe 8 bits, c. 1978 (jamais publié) |

| TMS9989 | 9980 amélioré, utilisé dans le matériel militaire |

| TMS9995 | TMS9985-like amélioré, pas de ROM. Utilisé dans les prototypes TI-99/2 & TI-99/8, le Tomy Tutor et l'ordinateur Geneve |

| TMS99105 | Membre de base de la famille de microprocesseurs TMS99000 |

| TMS99110 | Microprocesseur de la famille TMS99000 avec instructions à virgule flottante préprogrammées dans la mémoire ROM Macrostore sur puce |

| TMS99120 | Microprocesseur de la famille TMS99000 avec des routines de support d'exécution pour le langage de haut niveau PASCAL préprogrammé dans la mémoire ROM Macrostore sur puce (le microprocesseur a été annoncé mais n'a peut-être jamais été produit commercialement) |

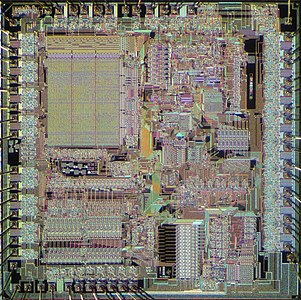

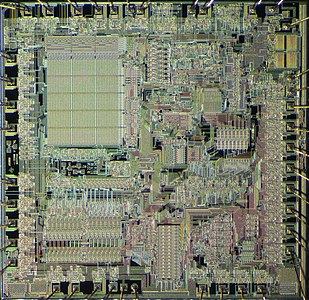

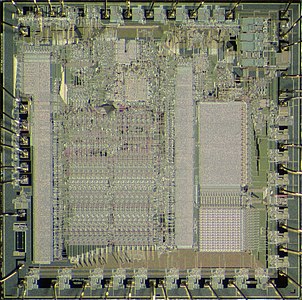

- Photos de matrices

Les références

Liens externes

- Manuels et références TMS9900 de Bitsavers