Convertisseur temps-numérique - Time-to-digital converter

Dans l' instrumentation électronique et le traitement du signal , un convertisseur temps-numérique ( TDC ) est un dispositif permettant de reconnaître des événements et de fournir une représentation numérique de l' heure à laquelle ils se sont produits. Par exemple, un TDC peut émettre l'heure d'arrivée pour chaque impulsion entrante. Certaines applications souhaitent mesurer l'intervalle de temps entre deux événements plutôt qu'une notion de temps absolu.

En électronique, les convertisseurs temps-numérique (TDC) ou les numériseurs de temps sont des dispositifs couramment utilisés pour mesurer un intervalle de temps et le convertir en sortie numérique (binaire). Dans certains cas, les TDC d' interpolation sont également appelés compteurs de temps (TC).

Les TDC sont utilisés pour déterminer l'intervalle de temps entre deux impulsions de signal (appelées impulsions de démarrage et d'arrêt). La mesure est démarrée et arrêtée lorsque le front montant ou descendant d'une impulsion de signal franchit un seuil défini. Ce schéma est observé dans de nombreuses expériences physiques, telles que les mesures du temps de vol et de la durée de vie en physique atomique et des hautes énergies , des expériences impliquant la télémétrie laser et la recherche électronique impliquant le test de circuits intégrés et le transfert de données à grande vitesse.

Application

Les TDC sont utilisés dans des applications où les événements de mesure se produisent rarement, comme les expériences de physique à haute énergie , où le grand nombre de canaux de données dans la plupart des détecteurs garantit que chaque canal ne sera excité que rarement par des particules telles que des électrons, des photons et des ions.

Mesure grossière

Si la résolution temporelle requise n'est pas élevée, des compteurs peuvent être utilisés pour effectuer la conversion.

Compteur de base

Dans sa mise en œuvre la plus simple, un TDC est simplement un compteur haute fréquence qui incrémente chaque cycle d'horloge. Le contenu actuel du compteur représente l'heure actuelle. Lorsqu'un événement se produit, la valeur du compteur est capturée dans un registre de sortie.

Dans cette approche, la mesure est un nombre entier de cycles d'horloge, donc la mesure est quantifiée à une période d'horloge. Pour obtenir une résolution plus fine, une horloge plus rapide est nécessaire. La précision de la mesure dépend de la stabilité de la fréquence d'horloge.

Typiquement, un TDC utilise une fréquence de référence d' oscillateur à cristal pour une bonne stabilité à long terme. Les oscillateurs à cristal à haute stabilité sont généralement des fréquences relativement basses telles que 10 MHz (ou une résolution de 100 ns). Pour obtenir une meilleure résolution, un multiplicateur de fréquence de boucle à verrouillage de phase peut être utilisé pour générer une horloge plus rapide. On pourrait, par exemple, multiplier l'oscillateur de référence à cristal par 100 pour obtenir une fréquence d'horloge de 1 GHz (résolution 1 ns).

Technologie de compteur

Des fréquences d'horloge élevées imposent des contraintes de conception supplémentaires au compteur : si la période d'horloge est courte, il est difficile de mettre à jour le compte. Les compteurs binaires, par exemple, ont besoin d'une architecture de report rapide car ils ajoutent essentiellement un à la valeur de compteur précédente. Une solution utilise une architecture de compteur hybride. Un compteur Johnson , par exemple, est un compteur non binaire rapide. Il peut être utilisé pour compter très rapidement le nombre d'ordres faibles ; un compteur binaire plus conventionnel peut être utilisé pour accumuler le compte d'ordre élevé. Le compteur rapide est parfois appelé prescaler .

La vitesse des compteurs fabriqués en technologie CMOS est limitée par la capacité entre la grille et le canal et par la résistance du canal et des traces de signal. Le produit des deux est la fréquence de coupure. La technologie moderne des puces permet d'insérer plusieurs couches métalliques et donc des bobines avec un grand nombre d'enroulements dans la puce. Cela permet aux concepteurs de mettre le dispositif au pic pour une fréquence spécifique , qui peut se situer au-dessus de la fréquence de coupure du transistor d'origine.

Une variante de pointe du compteur Johnson est le compteur d' ondes progressives qui atteint également une résolution de sous-cycle. D'autres méthodes pour obtenir une résolution de sous-cycle incluent les convertisseurs analogique-numérique et les compteurs à vernier Johnson .

Mesurer un intervalle de temps

Dans la plupart des situations, l'utilisateur ne souhaite pas simplement capturer une heure arbitraire à laquelle un événement se produit, mais souhaite mesurer un intervalle de temps, le temps entre un événement de début et un événement d'arrêt.

Cela peut être fait en mesurant un temps arbitraire à la fois des événements de début et de fin et en soustrayant. La mesure peut être erronée de deux points.

La soustraction peut être évitée si le compteur est maintenu à zéro jusqu'à l'événement de début, compte pendant l'intervalle, puis arrête de compter après l'événement d'arrêt.

Les compteurs grossiers reposent sur une horloge de référence avec des signaux générés à une fréquence stable . Lorsque le signal de démarrage est détecté, le compteur commence à compter les signaux d'horloge et termine le comptage après la détection du signal d'arrêt. L'intervalle de temps entre le démarrage et l'arrêt est alors

avec , le nombre de coups et , la période de l' horloge de référence .

Compteur statistique

Étant donné que les signaux de démarrage, d'arrêt et d' horloge sont asynchrones, il existe une distribution de probabilité uniforme des temps de signal de démarrage et d'arrêt entre deux impulsions d'horloge ultérieures. Ce désaccord du signal de démarrage et d'arrêt à partir des impulsions d'horloge est appelé erreur de quantification .

Pour une série de mesures sur le même intervalle de temps constant et asynchrone, on mesure deux nombres différents d'impulsions d'horloge comptées et (voir image). Ceux-ci se produisent avec des probabilités

avec la partie fractionnaire de . La valeur de l'intervalle de temps est alors obtenue par

La mesure d'un intervalle de temps à l'aide d'un compteur grossier avec la méthode de calcul de moyenne décrite ci-dessus prend relativement beaucoup de temps en raison des nombreuses répétitions nécessaires pour déterminer les probabilités et . Par rapport aux autres méthodes décrites plus loin, un compteur grossier a une résolution très limitée (1ns dans le cas d'une horloge de référence à 1 GHz ), mais satisfait à sa plage de mesure théoriquement illimitée.

Mesure fine

Contrairement au compteur grossier de la section précédente, des méthodes de mesure fine avec une bien meilleure précision mais une plage de mesure beaucoup plus petite sont présentées ici. Des méthodes analogiques comme l'étirement de l'intervalle de temps ou la double conversion ainsi que des méthodes numériques comme les lignes à retard à prises et la méthode Vernier sont à l'étude. Bien que les méthodes analogiques obtiennent toujours de meilleures précisions, la mesure d'intervalle de temps numérique est souvent préférée en raison de sa flexibilité dans la technologie des circuits intégrés et de sa robustesse contre les perturbations externes telles que les changements de température.

La précision de l'implémentation du compteur est limitée par la fréquence d'horloge. Si le temps est mesuré en nombres entiers, la résolution est limitée à la période d'horloge. Par exemple, une horloge de 10 MHz a une résolution de 100 ns. Pour obtenir une résolution plus fine qu'une période d'horloge, il existe des circuits d'interpolation temporelle. Ces circuits mesurent la fraction d'une période d'horloge : c'est-à-dire le temps entre un événement d'horloge et l'événement mesuré. Les circuits d'interpolation nécessitent souvent un temps important pour remplir leur fonction ; par conséquent, le TDC a besoin d'un intervalle calme avant la prochaine mesure.

Interpolateur de rampe

Lorsque le comptage n'est pas possible car la fréquence d'horloge serait trop élevée, des méthodes analogiques peuvent être utilisées. Les méthodes analogiques sont souvent utilisées pour mesurer des intervalles compris entre 10 et 200 ns. Ces méthodes utilisent souvent un condensateur qui est chargé pendant l'intervalle mesuré. Initialement, le condensateur est déchargé à zéro volt. Lorsque l'événement de démarrage se produit, le condensateur est chargé avec un courant constant I 1 ; le courant constant fait que la tension v sur le condensateur augmente linéairement avec le temps. La tension montante est appelée rampe rapide. Lorsque l'événement d'arrêt se produit, le courant de charge est arrêté. La tension sur le condensateur v est directement proportionnelle à l'intervalle de temps T et peut être mesurée avec un convertisseur analogique-numérique (ADC). La résolution d'un tel système est de l'ordre de 1 à 10 ps.

Bien qu'un ADC séparé puisse être utilisé, l'étape ADC est souvent intégrée dans l'interpolateur. Un deuxième courant constant I 2 est utilisé pour décharger le condensateur à une vitesse constante mais beaucoup plus lente (la rampe lente). La rampe lente peut être 1/1000 de la rampe rapide. Cette décharge "étire" effectivement l'intervalle de temps ; il faudra 1000 fois plus de temps pour que le condensateur se décharge à zéro volt. L'intervalle étiré peut être mesuré avec un compteur. La mesure est similaire à un convertisseur analogique à double pente .

La conversion à double pente peut prendre beaucoup de temps : un millier de tics d'horloge dans le schéma décrit ci-dessus. Cela limite la fréquence à laquelle une mesure peut être effectuée (temps mort). Une résolution de 1 ps avec une horloge de 100 MHz (10 ns) nécessite un taux d'étirement de 10 000 et implique un temps de conversion de 150 µs. Pour diminuer le temps de conversion, le circuit interpolateur peut être utilisé deux fois dans une technique d'interpolateur résiduel . La rampe rapide est utilisée initialement comme ci-dessus pour déterminer le temps. La rampe lente n'est qu'à 1/100. La rampe lente traversera zéro à un moment donné pendant la période d'horloge. Lorsque la rampe passe à zéro, la rampe rapide est réactivée pour mesurer le temps de franchissement ( t résiduel ). Par conséquent, le temps peut être déterminé à 1 partie sur 10 000.

Les interpolateurs sont souvent utilisés avec une horloge système stable. L'événement de démarrage est asynchrone, mais l'événement d'arrêt est une horloge suivante. Pour plus de commodité, imaginez que la rampe rapide augmente d'exactement 1 volt pendant une période d'horloge de 100 ns. Supposons que l'événement de démarrage se produise à 67,3 ns après une impulsion d'horloge ; l'intégrateur de rampe rapide est déclenché et commence à monter. L'événement de démarrage asynchrone est également acheminé via un synchroniseur qui prend au moins deux impulsions d'horloge. À la prochaine impulsion d'horloge, la rampe est montée à 0,327 V. À la deuxième impulsion d'horloge, la rampe est montée à 1,327 V et le synchroniseur signale que l'événement de démarrage a été vu. La rampe rapide est arrêtée et la rampe lente démarre. La sortie du synchroniseur peut être utilisée pour capturer l'heure du système à partir d'un compteur. Après 1327 horloges, la rampe lente revient à son point de départ et l'interpolateur sait que l'événement s'est produit 132,7 ns avant que le synchroniseur ne le signale.

L'interpolateur est en fait plus impliqué car il y a des problèmes de synchroniseur et la commutation de courant n'est pas instantanée. De plus, l'interpolateur doit calibrer la hauteur de la rampe sur une période d'horloge.

Vernier

Interpolateur Vernier

La méthode vernier est plus complexe. Le procédé implique un oscillateur déclenchable et un circuit de coïncidence. Lors de l'événement, le compte d'horloge entier est stocké et l'oscillateur est démarré. L'oscillateur déclenché a une fréquence légèrement différente de celle de l'oscillateur d'horloge. Par souci d'argument, disons que l'oscillateur déclenché a une période qui est 1 ns plus rapide que l'horloge. Si l'événement s'est produit 67 ns après la dernière horloge, la transition d'oscillateur déclenchée glissera de -1 ns après chaque impulsion d'horloge suivante. L'oscillateur déclenché sera à 66 ns après la prochaine horloge, à 65 ns après la deuxième horloge, et ainsi de suite. Un détecteur de coïncidence recherche le moment où l'oscillateur déclenché et l'horloge passent en même temps, et cela indique la fraction de temps qui doit être ajoutée.

La conception de l'interpolateur est plus complexe. L'horloge déclenchable doit être calibrée sur l'horloge. Il doit également démarrer rapidement et proprement.

Méthode Vernier

La méthode Vernier est une version numérique de la méthode d'étirement du temps. Deux oscillateurs seulement légèrement désaccordés (avec des fréquences et ) démarrent leurs signaux avec l'arrivée du signal de départ et du signal d'arrêt. Dès que les fronts montants des signaux de l' oscillateur coïncident, la mesure se termine et le nombre de périodes des oscillateurs ( respectivement et ) conduit à l'intervalle de temps d'origine :

Étant donné que les oscillateurs hautement fiables avec une fréquence stable et précise sont toujours un défi, on réalise également la méthode du vernier via deux lignes à retard à prises utilisant deux temps de retard de cellule légèrement différents . Ce réglage est appelé ligne à retard différentiel ou ligne à retard vernier .

Dans l'exemple présenté ici, la première ligne à retard affiliée au signal de démarrage contient des cellules de bascules D à retard qui sont initialement réglées sur transparentes. Pendant la transition du signal de démarrage à travers l'une de ces cellules, le signal est retardé de et l'état de la bascule est échantillonné comme transparent. La deuxième ligne à retard appartenant au signal d'arrêt est composée d'une série de tampons non inverseurs à retard . En se propageant dans son canal, le signal d'arrêt verrouille les bascules de la ligne à retard du signal de démarrage. Dès que le signal d'arrêt passe le signal de démarrage, celui-ci est arrêté et toutes les bascules restantes sont échantillonnées de manière opaque. De manière analogue au cas ci-dessus des oscillateurs, l'intervalle de temps souhaité est alors

avec n le nombre de cellules marquées comme transparentes.

Ligne à retard taraudée

En général, une ligne à retard à prises contient un certain nombre de cellules avec des temps de retard bien définis . En se propageant à travers cette ligne, le signal de démarrage est retardé. L'état de la ligne est échantillonné au moment de l'arrivée du signal d'arrêt. Ceci peut être réalisé par exemple avec une ligne de cellules D-flip-flop avec un temps de retard . Le signal de démarrage se propage dans cette ligne de bascules transparentes et est retardé d'un certain nombre d'entre elles. La sortie de chaque bascule est échantillonnée à la volée. Le signal d'arrêt verrouille toutes les bascules tout en se propageant à travers son canal sans retard et le signal de démarrage ne peut pas se propager davantage. Maintenant, l'intervalle de temps entre le signal de démarrage et d'arrêt est proportionnel au nombre de bascules qui ont été échantillonnées comme transparentes.

Mesure hybride

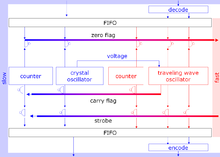

Les compteurs peuvent mesurer de longs intervalles mais ont une résolution limitée. Les interpolateurs ont une haute résolution mais ils ne peuvent pas mesurer de longs intervalles. Une approche hybride peut atteindre à la fois de longs intervalles et une haute résolution. Le long intervalle peut être mesuré avec un compteur. Les informations du compteur sont complétées par deux interpolateurs de temps : un interpolateur mesure l'intervalle (court) entre l'événement de démarrage et un événement d'horloge suivant, et le second interpolateur mesure l'intervalle entre l'événement d'arrêt et un événement d'horloge suivant. L'idée de base a quelques complications : les événements de démarrage et d'arrêt sont asynchrones, et l'un ou les deux peuvent se produire à proximité d'une impulsion d'horloge. Le compteur et les interpolateurs doivent se mettre d'accord pour faire correspondre les événements d'horloge de début et de fin. Pour atteindre cet objectif, des synchroniseurs sont utilisés.

L'approche hybride courante est la méthode Nutt . Dans cet exemple, le circuit de mesure fine mesure le temps entre l'impulsion de démarrage et d'arrêt et la deuxième impulsion d'horloge la plus proche respective du compteur grossier ( T start , T stop ), détecté par le synchroniseur (voir figure). Ainsi, l'intervalle de temps souhaité est

avec n le nombre d'impulsions d'horloge du compteur et T 0 la période du compteur grossier.

Histoire

La mesure du temps a joué un rôle crucial dans la compréhension de la nature depuis les temps les plus reculés. En commençant par les horloges à soleil, à sable ou à eau , nous pouvons aujourd'hui utiliser des horloges basées sur les résonateurs au césium les plus précis .

Le premier prédécesseur direct d'un TDC a été inventé en 1942 par Bruno Rossi pour mesurer la durée de vie des muons . Il a été conçu comme un convertisseur temps-amplitude , chargeant constamment un condensateur pendant l'intervalle de temps mesuré. La tension correspondante est directement proportionnelle à l'intervalle de temps examiné.

Alors que les concepts de base (comme les méthodes Vernier ( Pierre Vernier 1584-1638) et l'étirement du temps) de division du temps en intervalles mesurables sont toujours d'actualité, la mise en œuvre a beaucoup changé au cours des 50 dernières années. En commençant par les tubes à vide et les transformateurs à noyau en ferrite, ces idées sont aujourd'hui mises en œuvre dans la conception complémentaire de métal-oxyde-semiconducteur ( CMOS ).

les erreurs

- Quelques informations de

Même en ce qui concerne les méthodes de mesure fines présentées, il existe encore des erreurs que l'on peut souhaiter supprimer ou au moins prendre en compte. Les non-linéarités de la conversion temps-numérique par exemple peuvent être identifiées en prenant un grand nombre de mesures d'une source distribuée poissonnienne (test de densité de code statistique). De petits écarts par rapport à la distribution uniforme révèlent les non-linéarités. Malheureusement, la méthode de densité de code statistique est assez sensible aux changements de température externes. Ainsi, des circuits à retard de stabilisation ou à boucle à verrouillage de phase (DLL ou PLL) sont recommandés.

De la même manière, les erreurs de décalage (lectures différentes de zéro à T = 0) peuvent être supprimées.

Pour de longs intervalles de temps, l'erreur due aux instabilités de l' horloge de référence ( gigue ) joue un rôle majeur. Ainsi, des horloges de qualité supérieure sont nécessaires pour de tels TDC.

De plus, les sources de bruit externes peuvent être éliminées en post-traitement par des méthodes d'estimation robustes .

Configurations

Les TDC sont actuellement construits en tant qu'appareils de mesure autonomes dans des expériences physiques ou en tant que composants système comme les cartes PCI. Ils peuvent être constitués de circuits discrets ou intégrés.

La conception du circuit change avec l'objectif du TDC, qui peut être une très bonne solution pour les TDC à un seul coup avec de longs temps morts ou un compromis entre le temps mort et la résolution pour les TDC à plusieurs coups.

Générateur de retard

Le convertisseur temps-numérique mesure le temps entre un événement de démarrage et un événement d'arrêt. Il existe également un convertisseur numérique-temps ou un générateur de retard . Le générateur de délai convertit un nombre en un délai. Lorsque le générateur de retard reçoit une impulsion de démarrage à son entrée, il émet une impulsion d'arrêt après le retard spécifié. Les architectures des générateurs de TDC et de retard sont similaires. Les deux utilisent des compteurs pour des délais longs et stables. Les deux doivent considérer le problème des erreurs de quantification d'horloge.

Par exemple, le délai numérique Tektronix 7D11 utilise une architecture de compteur. Un retard numérique peut être réglé de 100 ns à 1 s par incréments de 100 ns. Un circuit analogique fournit un retard fin supplémentaire de 0 à 100 ns. Une horloge de référence de 5 MHz entraîne une boucle à verrouillage de phase pour produire une horloge stable de 500 MHz. C'est cette horloge rapide qui est déclenchée par l'événement de démarrage (finement retardé) et détermine l'erreur de quantification principale. L'horloge rapide est divisée à 10 MHz et alimentée au compteur principal. L'erreur de quantification de l'instrument dépend principalement de l'horloge à 500 MHz (pas de 2 ns), mais d'autres erreurs entrent également ; l'instrument est spécifié pour avoir 2,2 ns de gigue . Le temps de recyclage est de 575 ns.

Tout comme un TDC peut utiliser l'interpolation pour obtenir une résolution plus fine qu'une période d'horloge, un générateur de retard peut utiliser des techniques similaires. Le synthétiseur temporel haute résolution Hewlett-Packard 5359A fournit des délais de 0 à 160 ms, a une précision de 1 ns et atteint une gigue typique de 100 ps. La conception utilise un oscillateur à verrouillage de phase déclenché qui fonctionne à 200 MHz. L'interpolation se fait avec une rampe, un convertisseur numérique-analogique 8 bits et un comparateur. La résolution est d'environ 45 ps.

Lorsque l'impulsion de démarrage est reçue, puis décompte et émet une impulsion d'arrêt. Pour une faible gigue, le compteur synchrone doit envoyer un indicateur zéro du bit le plus significatif au bit le moins significatif , puis le combiner avec la sortie du compteur Johnson.

Un convertisseur numérique-analogique (DAC) pourrait être utilisé pour obtenir une résolution de sous-cycle, mais il est plus facile d'utiliser des compteurs à vernier Johnson ou des compteurs Johnson à ondes progressives.

Le générateur de retard peut être utilisé pour la modulation de largeur d'impulsion , par exemple pour piloter un MOSFET afin de charger une cellule de Pockels en 8 ns avec une charge spécifique.

La sortie d'un générateur de retard peut déclencher un convertisseur numérique-analogique et ainsi des impulsions d'une hauteur variable peuvent être générées. Cela permet de faire correspondre les niveaux bas requis par l'électronique analogique, des niveaux plus élevés pour l' ECL et des niveaux encore plus élevés pour le TTL . Si une série de CNA est déclenchée en séquence, des formes d'impulsion variables peuvent être générées pour tenir compte de toute fonction de transfert.

Voir également

Les références

Liens externes

- US 3983481 , Nutt, Ronald; Kelly Milam & Charles W. Williams, "Intervallomètre numérique", publié le 4 août 1975, publié le 18 septembre 1976

- US 3133189 , Bagley, Alan S. & Merrill W. Brooksby, "Electronic Interpolating Counter for the Time Interval and Frequency Measurement", publié le 5 août 1960, délivré le 12 mai 1964

- US 2665411 , Frady, William E., Jr., "Double Interpolation Method and Apparatus for Measuring Time Intervals", publié le 15 mars 1951, publié le 5 janvier 1954

- US 2665410 , Burbeck, Donald W., "Method and Apparatus for Automatically Measuring Time Intervals", publié le 15 mars 1951, publié le 5 janvier 1954

- US 2560124 , Mofenson, Jack, "Interval Measuring System", publié le 31 mars 1950, publié le 10 juillet 1951

- http://www.freepatentsonline.com/8324952.html

- CMOS à ondes progressives

- onde progressive nFET cascode

- http://www.febo.com/pages/hp5370b/

- http://www.g8wrb.org/useful-stuff/time/HP-5370B/

- http://ilrs.gsfc.nasa.gov/docs/timing/artyukh_time_interval_counter.pdf

- http://ilrs.gsfc.nasa.gov/docs/time_interval_measurements.pdf

- http://tycho.usno.navy.mil/ptti/1994/Vol%2026_22.pdf

- http://www.acam.de/fileadmin/Download/pdf/English/AN002_e.pdf

- Salvatore, Loffredo (2010), Conception, construction et tests d'un convertisseur temps-numérique haute résolution et plage dynamique élevée Università degli studi Roma Tre, Scuola Dottorale in Scienze Matematiche e Fisiche

- Kalisz, Jozef; Szplet, Ryszard ; Pelka, Ryszard (août 1997), "Compteur de temps d'interpolation à puce unique avec résolution de 200 ps et plage de 43 s", Transactions IEEE sur l'instrumentation et la mesure , IEEE, 46 (4) : 851–856, doi : 10.1109/19.650787 , ISSN 0018-9456

- http://www.ti.com/lit/ds/symlink/tdc7200.pdf